I3C Protocol Analyzer and Exerciser

I3C Protocol Analyzer (PGY-I3C-EX-PD) is the Protocol Analyzer with multiple features to capture and debug communication between host and design under test. I3C Serial bus interface is emerging as a chosen interface for all future sensor connectivity in mobile phone and automotive industries. This could also be chosen as a low-cost, reliable interface for future embedded electronic applications to address the new data-intensive applications.

The PGY-I3C-EX-PD is the leading instrument that enables the design and test engineers to test the I3C designs for their specifications by configuring the PGY-I3C-EX-PD as Master/Slave to generate I3C traffic with error injection capabilities and to decode I3C protocol packets.

Key features

- Supports v1.0/v1.1/v1.1.1 Specifications*.

- Ability to configure it as Master or Slave.

- Ability to configure BCR, LVR, and DCR registers.

- Simultaneously generate I3C traffic and Protocol decode of the Bus.

- Optional Compliance Test Specifications (CTS) test script support.

- Supports legacy I2C slaves and masters.

- Generate different I3C SDR and HDR Packets.

- Supports IBI and Hot Plug capabilities.

- Error Injection such as CRC errors, parity errors, and ACK/NACK errors.

- Variable I3C data speeds and duty cycle.

- PMIC device support as per JEDEC DDR5 spec requirement.

- Margin test capability: Voltage and timing variation.

- Continuous streaming of protocol data between the instrument and host computer.

- Timing diagram of Protocol decoded bus.

- Listing view of Protocol activity.

- Error Analysis in Protocol Decode.

- Ability to write exerciser script to combine multiple data frame generation at different data speeds.

- USB2/3 host computer interface.

- API support for automation in Python or C++.

*v1.1/v1.1.1 supports only one-lane commands

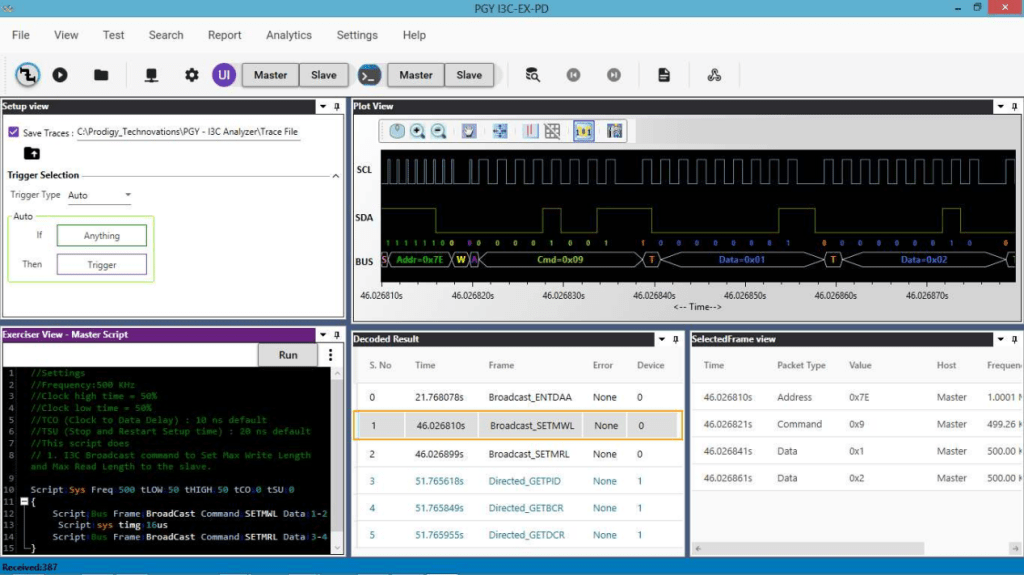

Multi-domain View

Multi-domain View provides the complete view of I3C Protocol activity in a single GUI. Users can easily set up the analyzer to generate I3C/I2C traffic using the GUI or script. Users can set different trigger conditions from the setup menu to capture protocol activity at specific events and decode the transition between the Master and Slave. The decoded results can be viewed in the timing diagram and protocol listing windows with auto-correlation. State machine view provides switching of state machine between master and slave for design validation. This comprehensive view of information makes it an industry-best offering and an easy-to-use solution to debug the I3C protocol activity.

Exerciser

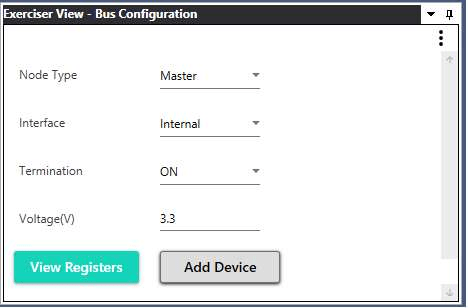

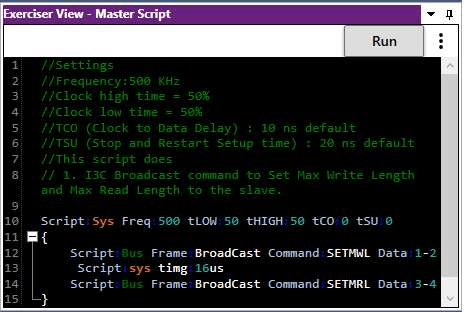

PGY-I3C-EX-PD supports I3C traffic generation using GUI and Script. Users can perform simple traffic generation using the GUI to test the DUT. Script-based GUI provides flexibility to emulate the complete expected traffic in the real world including error injections. In the below sample script users can generate I3C traffic as below:

Script line #10: Set system Frequency 500KHz, Duty cycle to 50%, CLK to data delay to 10ns (default), start to restart setup time to 20ns (default)

Script line #12: SETMWL

Script line #13: Set system inter message gap to 16us

Script line #14: SETMRL

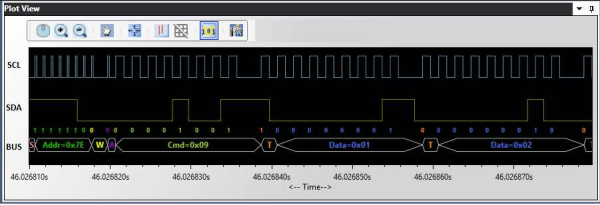

Timing Diagram and Protocol Listing View

The timing view provides the plot of SCL and SDA signals with bus diagram information. Overlayingofprotocol bits on the digital timing waveform helps in the easy debugging of protocol decoded data. Cursor and zoom features make it convenient to analyze protocol in timing diagrams for any timing error.

The protocol window provides the decoded packet information in each state and all packet details with error info in the packet. The selected frame in the protocol listing window will be auto-correlated in the timing view to view the timing information of the packet.

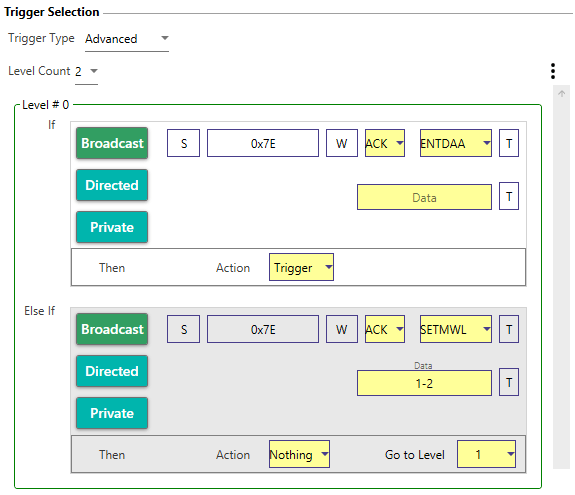

Powerful Trigger Capabilities

PGY-I3C-EX-PD supports auto, simple, and advanced trigger capabilities. The analyzer can trigger any of the protocol packets such as broadcast, directed, or private messages. Advanced trigger provides the flexibility to monitor multiple trigger conditions and can set multiple state trigger machines.

PGY-I3C-EX-PD Specification

Exerciser | |

Configurable | 1 Master + 3 Slaves or 1 Secondary Master + 2 Slaves |

I3C/I2C Traffic Generation | Custom I3C/I2C traffic generation (Simulate real world network traffic) |

SCL Frequency | 1Hz to 12.5MHz Note: Prodigy device supports up to 10MHz at 1V frequency as a slave |

Configurable Voltage Level Drive | 0.9V to 3.4V Steps: 0.9-1.27V (In steps of 5mV) 1.27-1.95V (In steps of 10mV) 1.95-3.4V (In steps of 30mV) |

Heat Join | Yes, supported |

IBI | Yes, supported |

CCC Support | All CCC are supported in the Master slide. All CCC are supported in Slave except SETXTIME, ENTTM, ENTAS* |

SCL Duty Cycle variation | User Defined (In Fine resolutions of 10ns) |

SCL & SDA Delay | User Defined (In Fine resolutions of 18ps) |

Delay between two messages | User Defined (In Fine resolutions of ns, us, ms and seconds) |

Error injection | S0 to S5 types of errors specified in BBC specifications CRC errors in DDR traffic. Preamble errors in DDR traffic ACK/NACK Errors (Slave) Master Abort. Non-Standard Frames. Non-Standard Start, Stop and HDR exit patterns, slave reset Save and Load Scripts. |

API Support | Support for Automation of operation using Python or C++ |

Protocol Analysis: | |

Supports | I3C & I2C protocol decode |

Protocol Views | Timing Diagram View Protocol Listing View Bus-Diagram to display Protocol packets with timing diagram plot |

Protocol Trigger | Auto (Trigger on any packet) Simple (Trigger on user defined I3C or I2C packet) |

Capture Duration | Continuous streaming Protocol Data to host HDD/SSD |

Protocol Error Report | S0 to S5 types of errors specified in the I3C specifications CRC errors in DDR traffic Preamble errors in DDR traffic ACK/NACK Errors (Slave) Master Abort Non-Standard frames Non-standard Start, Stop and HDR exit patterns. |

Host Connectivity | USB 3.0/2.0 interface |

I3C Protocol Analyzer and Exerciser – FAQ Section

Yes, PGY-I3C-EX-PD has support for API using Python and C++.

The PGY-I3C-EX-PD unit is field upgradable using firmware upgrades.

During warranty, the first level support is offered over emails/phone/WebEx. If physical support/repair is required, the unit needs to be shipped back to Prodigy India office. Where if we find the hardware faulty, we will repair/replace the unit under warranty.

Yes, PGY-I3C-EX-PD will have support for CTS v1.1.1 under which almost 90 test cases are included. Being a contributing member to MIPI, we have our CTS suite ready with the provisional specs, but the final document is still under review and it is expected to be ratified by MIPI soon. Hence, the Opt CTS (v1.1) delivery is subject to MIPI ratification. Once released, this option will also be post purchase – field upgradable for all existing customers.

The bus voltage can be varied from 1.0 V to 3.3V in steps of 50mV.

The PGY-I3C-EX-PD comes with a standard 12 months return to Prodigy warranty on the hardware and 12 months software support. Upfront hardware warranty & software support extension is possible for additional 24 Months. Accessories, cables & Probes are covered under 90 days warranty for any manufacturing defect only.

PGY-I3C-EX-PD has support for 1 Master + 3 slaves or 1 Master + 1 Secondary master and 2 slaves internally.

Similar Products